ramp buffer和三角波发生器

你能不能再帮我整理一份有关于Buck芯片中的控制部分需要三角波ramp和运放的输出进行运算产生PWM控制信号,这里的ramp的buffer电路和三角波电路如何设计的集成电路设计的相关内容,请给出具体的参考资料

好的,下面我整理一份专门针对在 Buck 转换器芯片中控制部分(即用三角/锯齿 ramp 波 + 运放误差信号 → 比较器 → PWM 产生)相关的 集成电路(IC)级设计 内容。包括:ramp 产生电路、buffer/调理电路、运放 + 比较器架构、注意事项、设计要点 + 参考资料。你可以把它作为模块化设计笔记。

一、模块概览

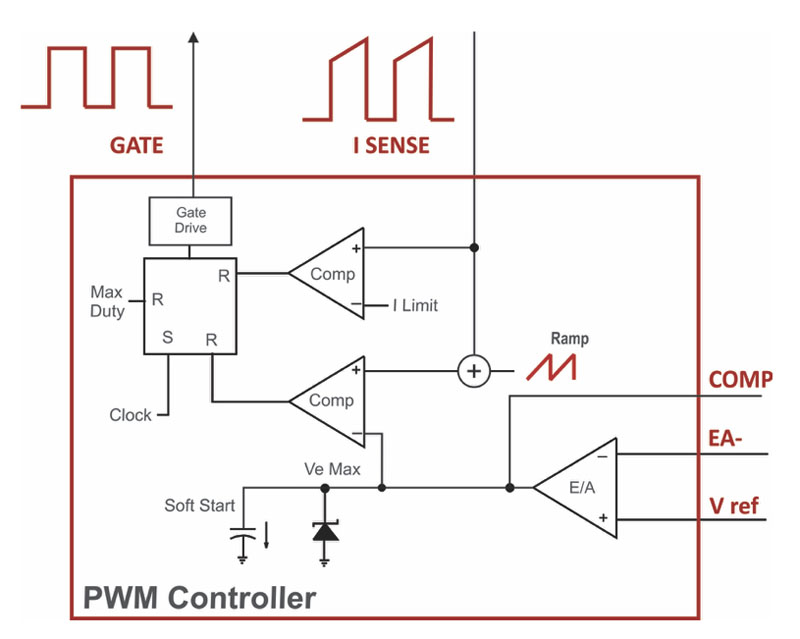

在一个典型的 Buck 控制 IC(尤其是电压模式或峰值电流模式)中,控制部分可简化为:

-

误差放大器(运放)输出一个误差信号 Verr。

-

产生一个固定频率的 ramp / 锯齿波 Vramp。

-

将 Verr 与 Vramp 送入比较器,比较器输出 PWM 信号 → 驱动开关管(MOSFET)。

-

在电流模式下,ramp 可能还叠加“斜坡补偿”(slope compensation)或受感测电流影响。

-

Buffer / 调理电路用于:使 Vramp 具备低输出阻抗、幅度与直流偏置正确、噪声低、共模匹配比较器输入。

下面我们分别拆模块讨论。

二、Ramp/锯齿波产生电路设计(集成电路级)

2.1 原理架构

-

一个恒流源 Icharge 对电容 Cramp 充电,从低电平 Vlow 向高电平 Vhigh 线性上升 → 得到斜坡。

-

到达 Vhigh 或检测到某事件(如周期触发)后,使用开关 Sreset 将 Cramp 快速放电或回到 Vlow ;然后下一个周期重复。

-

输出即为 Vramp(t) —— 通常从 Vlow → Vhigh 线性,再回零或低电平。

-

可通过改变 Icharge、Cramp、阈值差 (ΔV = Vhigh–Vlow) 来调节频率和斜率。

-

在某些结构中(尤其电流模式控制)ramp 的 斜率或振幅 会依据感测电流或其他信号被调节,用以实现 slope compensation。 例如专利:由感测电流影响 ramp 幅度或斜率。 (谷歌专利)

-

比如 “Low-Power CMOS Ramp Generator…” 一文里描述了一个 0.5 µm CMOS 中用于 Buck 的 ramp 生成器。 (Rincón-Mora教授网站)

2.2 集成电路设计关键点

-

恒流源的精度与温度漂移,决定 ramp 斜率稳定性。

-

电容 Cramp 尽量做为 on-chip MIM/Poly-cap,以减温漂,并确保线性充电区域足够。

-

放电开关 Sreset 要快速、干净,残余电荷与回路延迟会造成斜顶、失真、频率漂移。 在 “Buffered Linear-Ramp Generator” 一文中提到,精确地复位是关键。 (模拟器件)

-

如果需要调节频率/斜率(如 IoT 小电流模式),可加入 trim bits 或可编程电流源。比如 “A Design of Ramp Generator With Ramp trimming Control Bits…” 中提到。 (ResearchGate)

-

在高频 Buck (例如几 MHz)中,ramp 生成器必须考虑 PVT (工艺/电压/温度)变化、噪声干扰、复位延迟、斜率误差及线性度。

-

注意 ramp 所用电压范围要与比较器/误差放大器的输入窗口兼容。

2.3 设计公式 / 估算

-

斜率: ( m = \dfrac{I_{\text{charge}}}{C_{\text{ramp}}} ) (假设从 0 到 ΔV)

-

周期: ( T = \dfrac{C_{\text{ramp}} \cdot \Delta V}{I_{\text{charge}}} + t_{\text{reset}} )

-

频率: ( f \approx \dfrac{1}{T} )

-

若设计需要注入 slope 补偿: ( m_{\text{effective}} = m + m_{\text{slopeComp}} )

2.4 示例电路结构图

(参考 “Low-Power CMOS Ramp Generator…” )

三、Buffer/调理电路设计(为 ramp 输出服务)

3.1 功能需求

-

把 Vramp 变成比较器所需幅度/偏置(可能需要偏置成例如 0.5 V→1.5 V 的窗口)。

-

提供低输出阻抗,驱动比较器输入并抑制尖峰耦合或寄生。

-

提供必要的匹配、噪声抑制、差分/单端转换(如果需要)以及共模水平调整。

-

在某些结构中,ramp 还可能与其他信号(例如感测电流或偏置电压)做求和或限幅,Buffer 电路可能集成这些功能。

3.2 常见电路实现方式

-

运放作为电压跟随器:简单、带宽好、输出阻抗低。

-

源随器/射极随器(MOS 源随/BJT 射极随):当幅度微调或偏置提升必要时使用。

-

带 RC 滤波的小串阻 + 电容:抑制耦合尖峰。

-

在 IC 中,Buffer 可采用高速 CMOS 输入缓冲器 +偏置网络,从 Vramp 节点到比较器输入。

3.3 IC设计注意事项

-

Buffer 的带宽要求:≥ 10× ramp 频率,以保证波形边沿足够陡峭。

-

斜率失真/输出摆幅压缩:运放/缓冲器必须考虑其 slew 率、输出摆幅、共模范围。

-

噪声耦合:ramp 通常低幅度、高速 → PCB/版图设计中须注意隔离高频开关节点。

-

偏置电平:确保 ramp 最低电平正确(复位后很低或接近零),以免比较器误判。

-

寄生电容/电阻:尤在 IC 版图中,Cramp、Buffer 输入节点与周围元件可能有寄生,影响斜率/幅度/稳定性。

3.4 示例结构图

四、运放(误差放大器) + 比较器 + PWM 生成链路设计

4.1 误差放大器(运放)

-

将输出电压经分压得到 Vfb,与参考电压 Vref 比较,误差 Verr = Vref – Vfb。

-

运放输出 Verr 输入比较器,与 Vramp 比较。

-

在集成器设计中,运放需具备:较低开关频率噪声、良好直流精度、稳定性、输出驱动能力。

-

布局中应考虑模拟/数字/功率区分离、敏感节点屏蔽、参考电压源噪声隔离。

4.2 比较器 + PWM 生成

-

比较器输入:Vramp(上升斜坡)与 Verr。 当 Verr > Vramp → 输出触发 → 关断开关 → 下一周期。

-

因而:占空比 ≈ (Verr – Vlow) / ΔVramp(简化模型)

-

在电流模式:比较器一端或两端会加入电流检测信号 + ramp (即斜坡补偿)→ 防止次谐振。参考 TI 文档 “Practical Considerations in Current Mode Power Supplies” (德州仪器)

-

PWM 输出可能驱动 MOSFET 栅极/门极驱动器,或者经门驱放大器。控制 IC 内一般含启动/保护/软启动/欠压/过流逻辑。

4.3 版图/系统设计注意事项

-

尽量将模拟控制电路(运放 + ramp + buffer)与功率开关节点物理隔离。

-

模拟电源、参考源应对地做良好接地,避免功率开关环回噪声进入控制环。

-

Ramp 生成、Buffer、比较器应在版图中放置靠近彼此,以减寄生引起的延迟和误差。

-

对于 ramp 斜率误差、温漂、工艺变化,要做 Monte Carlo/PVT 分析。

-

测试插桩:设计中应考虑 ramp 波形观测节点、缓冲器输出、斜坡补偿注入点,以便量测和调试。

五、综合参考资料(文献+应用笔记)

-

H. Pooya Forghani-zadeh & G. Rincón-Mora, “Low-Power CMOS Ramp Generator Circuit for DC-DC Converters”, 0.5 µm CMOS 实例。 (图像之家)

-

TI 应用笔记 “Practical Considerations in Current Mode Power Supplies” — 讨论电流模式控制、斜坡补偿、ramp 生成机制。 (德州仪器)

-

TI 应用笔记 “Accuracy-Enhanced Ramp-Generation Design for D-CAP3 Modulation” — 针对 ramp 偏移、精度提升。 (德州仪器)

-

Microchip “TB3140 Programmable Ramp Generator Technical Brief” — 可编程 ramp 发生器设计思路。 (Microchip)

-

会议论文 “A Design of Ramp Generator With Ramp trimming Control Bits in DC-DC Buck Converter for IoT Applications” — 调频/斜率修正 ramp 生成设计。 (ResearchGate)

-

Analog Devices “Buffered Linear-Ramp Generator Operates Rail-to-Rail from a Single Supply” — buffer + ramp 生成参考。 (模拟器件)

-

专利 “Ramp generation in buck converters” (US11973425B2) — 集成电路中 ramp 受感测电流影响的方案。 (谷歌专利)

六、建议你的下一步动作

-

根据你的 Buck 芯片设计规格(例如开关频率、最大占空比、控制器输入参考电压范围)先 定义 Vramp 的 ΔV 范围、频率、斜率。

-

量化 Cramp 与 Icharge :输入工艺节点(如 0.18 µm、0.13 µm、65 nm)可用的 on-chip 电容和电流源。

-

给 buffer 电路选型:确定运放/缓冲器性能目标(带宽、输出摆幅、偏置范围)并仿真。

-

在版图早期分区:控制电路(误差放大器、ramp、buffer、比较器)与功率开关区分离、控制地与功率地分割、敏感节点屏蔽。

-

做 PVT 和 Monte Carlo 分析:主要看 ramp 斜率/幅度变化、buffer 输出驱动能力、比较器触发精度。

-

在 仿真中,观察 Vramp、Verr、占空比、开关节点波形,验证 PWM 产生机制是否符合规格。

如果你愿意,我可以 为你查找并整理几份“完整控制器 IC”厂商设计资料(包括 ramp 生成、buffer 结构、版图注意事项、标准cell 库)+ 提供一份 Cadence/Spice 可用的 ramp 生成参考电路,你看要不要?

好,我帮你整理了几份 关于 Buck 控制器 IC 中 ramp/三角波生成 + buffer 电路 +误差放大器/比较器部分 的参考资料,包括 集成电路级(on-chip)设计思路和应用笔记。你可以从中挑选若干全文下载、做深度阅读。

📄 推荐资料

-

Low‑Power CMOS Ramp Generator Circuit for DC‑DC Converters (Forghani-Zadeh & Rincon-Mora)

-

链接:由 Georgia Tech 提供,说明了一个 in-chip CMOS ramp 发生器(充电电流源 + 内部电容 +重置开关)在 0.5 µm 工艺中的实现。(Rincón-Mora 教授网站)

-

包括:ramp 的幅度精度、频率控制、复位问题、功耗设计。

-

适合:你想做 ramp 模块(电容、电流源、开关、阈值比较器)时,参考其结构、参数和工艺考量。

-

-

A Buck Converter Control Cookbook (Alpha & Omega Semiconductor)

-

链接:关于 Buck 转换器控制环路、反馈、ramp 注入、小信号建模等。(Alpha & Omega Semiconductor)

-

虽然不完全专注于 ramp buffer 电路,但解释了控制器中 ramp /补偿斜坡(slope compensation)如何与占空比、误差放大器、反馈环路交互。

-

对你理解运放输出 + ramp 比较 → PWM 的那条链路非常有帮助。

-

-

Transient Response Comparison of AECM with D‑CAP2 and PCM Control (TI)

-

链接:讨论 ramp 或“emulated ramp”在控制器 IC 内部如何实现、其对负载瞬态响应的影响。(德州仪器)

-

可用于:理解 控制器 IC 内部 ramp 生成方式(不是你外部做,而是集成在 IC 内)和 buffer、比较器、驱动链路。

-

-

Modeling and Loop Compensation Design of Switching Mode Power Supplies (Analog Devices – AN-149)

-

链接:虽然更偏环路补偿,但其中有提到 PWM 生成的调制器(含 ramp/triangle 比较器)和 Vosc(振荡器峰-峰电压)如何影响环路设计。(Analog Devices)

-

对你做整体控制器 IC 设计,理解 ramp 幅度、比较器输入电压窗、误差放大器输出范围等非常重要。

-

-

Quick Reference Guide to TI Buck Switching DC/DC Application Notes (TI)

-

链接:TI 整理的资料大全,其中包含“不同控制模式”、“Fixed-frequency vs Variable-frequency”、“控制器内 ramp/斜坡生成”概览。(德州仪器)

-

用途:快速定位你需要查的方向(比如固定频率电压模式控制→ramp 幅度;峰值电流模式→斜坡补偿)并找到具体厂商资料。

-

🧩 下一步建议

-

下载上面资料中的 第 1 条(ramp 生成器) 与 第 2 条(控制器 cookbook),仔细阅读其电路图、元件选型、参数推导。

-

在你的规格(例如:开关频率、ramp 幅值、比较器输入电压、运放输出范围)下,用第 1 条的原理 初步设计:确定 Cramp、Icharge、阈值 Vlow/Vhigh。

-

设计 buffer 电路:基于你的工艺选择一个高速运放或 CMOS 缓冲门,确认带宽、摆幅、偏置与电源要求。然后仿真。

-

将运放+ramp+比较器链路整合,做 Spice 或 Cadence 模拟:观察 Verr、Vramp、PWM 输出、斜坡变化、误差敏感度。

-

在版图阶段,参考上述应用笔记中的布局提示(模拟区隔、噪声隔离、寄生控制等)来布置 ramp 模块 + buffer +比较器。

如果你愿意,我可以 找出具体几个知名控制器 IC (如 TI、Analog Devices、Infineon)内部 ramp/buffer 模块的版图或专利,并把连接这些资料的下载链接整理给你。你看要不要?

下面是我为你整理的 几份知名 Buck/Buck-Boost 控制器 IC/功率转换器中关于 ramp(三角/锯齿波)生成 + 缓冲/调理 + 比较器/PWM 链路 的专利资料。你可以从中直接下载全文,查找其中的版图示例、buffer 结构、电容/电阻选型、逻辑控制电路等,有助于你 IC 设计时参考。

📑 推荐专利资料

-

US11973425B2 (“Ramp generation in buck converters”)

-

链接:Google Patents 页面。 (Google 专利)

-

内容概况:本发明提出一种功率转换器(例如 Buck)中集成的 ramp 生成电路,ramp 信号不仅基于控制信号,还基于输入电压和输出电压。(trea.com)

-

值得研究的点:

-

“ramp generator circuit … passive impedance circuit (without amplifying operation) and utilizes the output signal Vo to generate the ramp signal VPSR” (Google 专利)

-

版图或结构中可能会展示如何实现低输出阻抗、如何融合功率级信号以改善瞬态响应。

-

-

用途:可以参考其 ramp 生成 + 注入方式,了解集成化控制器中如何做 ramp 而不仅仅是外部简单充电电容结构。

-

-

US12334811B2 (“Closed loop stability ramp implementation for Constant On‐Time buck …”)

-

链接:Google Patents。 (Google 专利)

-

内容概况:主要针对 COT(Constant On-Time)控制模式下的 ramp 补偿方案,讨论闭环稳定性。

-

值得研究的点:

- 查看其如何在内部实现 ramp (或称斜坡补偿)、逻辑控制、如何与开关时间/占空比挂钩。

-

用途:如果你的设计是 COT 模式或混合模式,该专利提供了较进阶的 ramp 设计视角。

-

-

US11463005B2 (“Ramp generator for buck/boost converters”)

-

链接:Google Patents。 (Google 专利)

-

内容概况:这份专利专注于 Buck-Boost 转换器中的 ramp 生成电路,包括“first and second ramp signals”以适应不同模式。

-

值得研究的点:

- 看到多模式(buck/boost)控制下 ramp 如何生成、如何切换、如何做 overlap control。

-

用途:当你的 IC 可能还支持多模式或未来扩展时,这份资料尤其有价值。

-

-

CN114696606A (“Ramp voltage generation circuit of buck-boost converter”)

🛠 如何利用这些资料

-

把每份专利 下载 PDF,重点查看其中的 “Detailed Description” 部分和 “Figures(图示)” 部分。通常会有块图、线路图、版图缩影。

-

在版图或结构图中标记下:

-

ramp 生成电容/充电电流源/复位开关结构;

-

buffer/驱动器/比较器输入结构(如果有的话);

-

注入/叠加路径(例如将输出电压或输入电压比例注入 ramp) —— 这些可能就是你 buffer/调理电路设计的参考。

-

-

比较不同专利中 ramp 幅度、频率控制方式、斜率补偿方式有何不同。以此为基础,再结合你的工艺节点、频率目标、功耗目标,得出你自己的 ramp+buffer 方案。

-

在你的 IC 版图阶段,用专利中提到的 低输出阻抗结构、寄生控制、复位开关布局 等做 checklist,以避免常见坑(如 ramp 斜率漂移、噪声耦合、缓冲驱动不足)。

如果你愿意,我可以 帮你查找并整理3-5份“公开版图截图”的资料”(即专利或论文中带有实际版图缩影),并把它们按 “ramp 生成模块”、“buffer 模块”、“比较器/PWM 链路” 分类整理成一个 PDF 给你。你看要不要?